CPU缓存一致性简述

CPU也是有缓存的,而且还是多级缓存,那么它肯定也会出现缓存一致性问题,本文将讨论CPU缓存一致性的解决方案,这有助于我们拓展学习

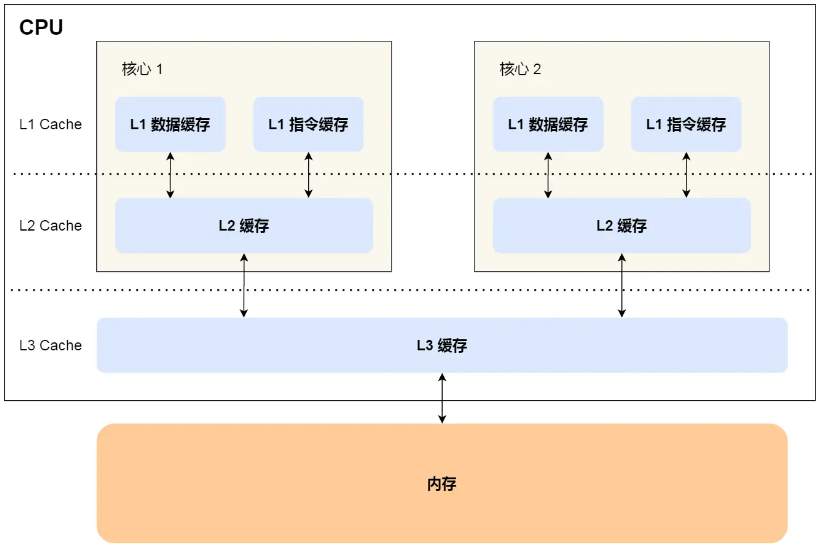

CPU缓存分级

CPU Cache通常分为三级,L1 Cache,L2 Cache, L3 Cache,L1离CPU核心最近,访问速度最快,存储容量最小,向外依次增加。

在多核心的CPU中,L1,L2每个核心都有,L3为共享缓存

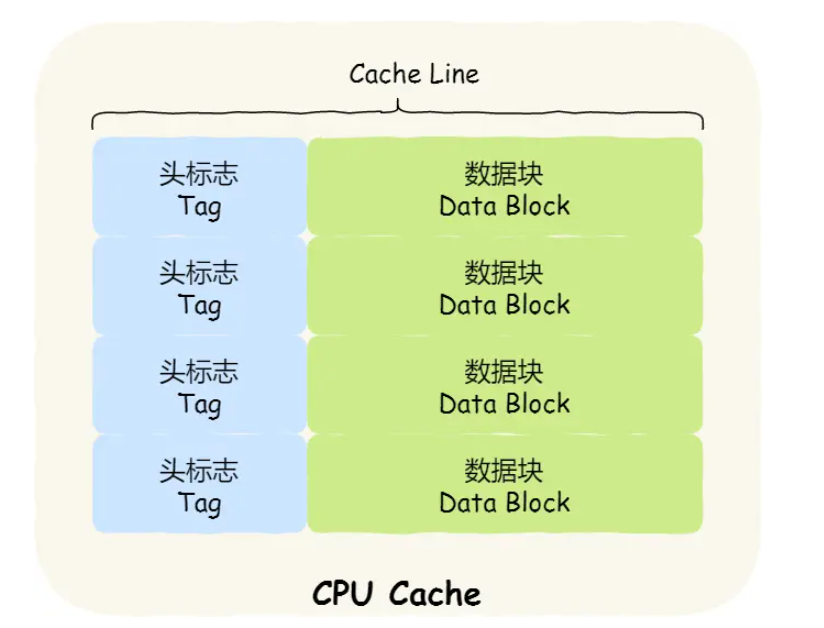

CPU Cache结构

CPU Cache由多个Cache Line组成,Cache Line时CPU从内存中读取数据的基本单位,由各种Tag + Data Block组成。

CPU Cache写入方式

写直达

保持缓存一致性最简单的方式就是一次写入,将数据同时写入内存和Cache中,这种方式称为写直达(Write Through)。

在这种写入模式下,对数据进行写操作之前会判断数据是否在CPU Cache中,如果在,先更新,再写入,不在的话,直接更新到内存中。

写直达实现简单,逻辑清晰,但是每次操作都会写内存,这没有充分发挥CPU Cache的高性能。

写回

为了降低访问内存的频率,出现了写回(Write Back)方法。

写回模式下,当发生写操作的时候,新的数据将会被写入Cache Line中,然后标记为脏数据,在该Cache Line被替换或系统要求(内存不足)的时候写回内存。

写回模式实现复杂,一致性较差,需要额外的标记位,但是性能高

CPU 缓存一致性问题

在多核模式下,如果有一个共享变量被多个核心同时操作,就会出现一致性问题。

如A,B同时操作变量 i = 0,A将变量增 1 , B也对变量增 1,这会出现两种问题

- A先更改,未写入缓存之前,B在初始值基础上增一,这会导致B的修改是错误的,A的修改被抹去。所以需要在写操作的时候进行消息传播,通知所有共享次变量的核心

- 多核同时操作的时候,比如还有C、D核心共享此变量,A、B的修改需要通知它们,而这个通知一定要保证操作顺序一致,也就是先A后B,不能出现先B后A的状况

所以要实现CPU缓存一致性,需要确保的就是两件事:

- 某个核心中的共享数据更新的时候,需要传播给其他核心,称为写传播(Write Propagation)

- 多个核心对数据的操作顺序,必须在其他核心看起来顺序是一样的,称为事务的串行化(Transaction Serialization)

总线嗅探 (写传播)

写传播要达到的目的就是当某个核心更新Cache中的数据后,要把该事件广播通知到其他核心,最常见的方式就是总线嗅探

总线嗅探的概念就是,所有CPU核心共享同一系统总线,通过缓存控制器监听总线活动,检测与本地缓存数据相关的操作,然后根据一致性协议采取相应行动

功能就是检测其他处理器的写操作并根据监听信息更新或失效本地缓存数据以保证缓存一致性。

MESI协议 一致性协议 事务串行化

MESI就是在总线嗅探下实现数据一致性的协议,它规定了数据的四种状态:

Modified 已修改

即脏标记,表示该数据被更新过

Exclusive 独占

即只有当前核心存储使用该数据,可以自由写入

Shared 共享

有多个核心共享相同数据,要更新的时候需要广播请求,将其它所有核心中对应的缓存无效

Invalid 无效

无效状态标识该数据失效,不可读取

本文中图片参考